# DM-OLED154-639

1.54" 128 x 64 Monochrome Graphic OLED Display Module-SPI

#### Contents

- 1 Revision History

- 2 Main Features

- 3 Pin Description

- 3.1 Panel Pin Description

- 3.2 Module Pin Description

- 4 Mechanical Drawing

- 4.1 Panel Mechanical Drawing

- 4.2 Module Mechanical Drawing

- 5 Electrical Characteristics

- 6 Optical Characteristics

- 7 AC characteristics

- 7.1 Serial Interface Timing Characteristics (4-wire SPI)

- 7.2 I2C interface characteristics

- 8 Power on/off sequence

- 9 Schematic

- 9.1 Module schematic

- 9.2 Application circuit for 4-wire SPI mode

- 9.3 Application circuit for IIC mode

- 10 Command Table

- 11 Reliability

- Warranty and Conditions

# 1 Revision History

| Date       | Changes       |

|------------|---------------|

| 2018-09-28 | First release |

## 2 Main Features

| Item             | Specification       | Unit   |

|------------------|---------------------|--------|

| Diagonal Size    | 1.54                | inch   |

| Display Mode     | Passive Matrix OLED | -      |

| Display Colors   | Monochrome          | Colors |

| Resolution       | 128 x 64            | pixel  |

| Controller IC    | SPD0301             | -      |

| Interface        | 4wire SPI           | -      |

| Active Area      | 35.052 x 17.516     | mm     |

| Module Dimension | 38.00 x 42.4        | mm     |

| Weight           | TBD                 | g      |

# 3 Pin Description

## 3.1 Panel Pin Description

| Pin No. | Symbol       | Function Description                                                                                                                                                  |                             |                            |  |  |  |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|--|--|--|

| 1111100 |              | Reserved Pin(Supporting                                                                                                                                               | Pin)                        |                            |  |  |  |

|         |              |                                                                                                                                                                       |                             | m stresses on the          |  |  |  |

| 1       | N.C. (GND)   | The supporting pins can reduce the influences from stresses on the function pins.                                                                                     |                             |                            |  |  |  |

| •       | 14.C. (GIVD) | These pins must be conne                                                                                                                                              | ected to external ground:   | as the ESD protection      |  |  |  |

|         |              | circuit.                                                                                                                                                              | ected to external ground    | as the ESD protection      |  |  |  |

|         |              | Ground of Analog Circui                                                                                                                                               | f                           |                            |  |  |  |

| 2       | VLSS         | This is an analog ground                                                                                                                                              |                             | ed to VSS externally       |  |  |  |

|         |              | Ground of Logic Circuit                                                                                                                                               | pin. it should be connect   | ed to VBB externally.      |  |  |  |

| 3       | VSS          |                                                                                                                                                                       | ets as a reference for the  | logic nine. It must be     |  |  |  |

| 3       | V 33         | VSS This is a ground pin. It acts as a reference for the logic pins. It must be connected to external ground.                                                         |                             |                            |  |  |  |

|         |              | Reserved Pin(Supporting                                                                                                                                               |                             |                            |  |  |  |

|         |              | The supporting pins can                                                                                                                                               |                             | m strasses on the          |  |  |  |

| 4       | N.C. (GND)   | function pins.                                                                                                                                                        | reduce the influences from  | in stresses on the         |  |  |  |

|         | N.C. (GND)   | These pins must be conne                                                                                                                                              | acted to external ground    | os the ESD protection      |  |  |  |

|         |              | circuit.                                                                                                                                                              | ected to external ground    | as the ESD protection      |  |  |  |

|         |              | Power Supply for Logic                                                                                                                                                |                             |                            |  |  |  |

| 5       | VDD          | This is a voltage supply p                                                                                                                                            | sin. It must be connected   | to external source         |  |  |  |

|         |              | Communicating Protocol                                                                                                                                                |                             | to external source.        |  |  |  |

|         |              | This pins are MCU interf                                                                                                                                              |                             | ha following table:        |  |  |  |

| 6       |              | This phis are weed intern                                                                                                                                             | BS1                         | BS2                        |  |  |  |

|         | BS1          | IIC                                                                                                                                                                   | _                           | 0                          |  |  |  |

|         | BS2          | 4-Wire SPI                                                                                                                                                            | 1                           | 0                          |  |  |  |

| 7       |              |                                                                                                                                                                       | 0                           | -                          |  |  |  |

| ,       |              | 8-bit 80XX parallel                                                                                                                                                   | 1                           | 1                          |  |  |  |

|         |              | 8-bit 68XX parallel                                                                                                                                                   | 0                           | 1                          |  |  |  |

|         | GG.          | Chip Select                                                                                                                                                           |                             | 1.6 2.6011                 |  |  |  |

| 8       | CS#          | This pin is the chip selec                                                                                                                                            |                             | ed for MCU                 |  |  |  |

|         |              | communication only who                                                                                                                                                |                             |                            |  |  |  |

| 0       | DEC#         | Power Reset for Controll                                                                                                                                              |                             |                            |  |  |  |

| 9       | RES#         | This pin is reset signal input. When the pin is low, initialization of the chip is executed. Keep this pin pull high during normal operation.                         |                             |                            |  |  |  |

|         |              |                                                                                                                                                                       | n pull nigh during norma    | operation.                 |  |  |  |

|         |              | Data/Command Control                                                                                                                                                  | 1 4 1 2 3371 41             |                            |  |  |  |

|         |              | This pin is Data/Comman                                                                                                                                               |                             |                            |  |  |  |

|         |              | input at D7~D0 is treated                                                                                                                                             |                             |                            |  |  |  |

|         |              | input at D7~D0 will be to                                                                                                                                             |                             |                            |  |  |  |

| 10      | D/C#         | When the pin is pulled high and serial interface mode is selected, the                                                                                                |                             |                            |  |  |  |

| 10      | D/C#         | at SDIN will be interpreted as data. When it is pulled low, the data at SDIN will be transferred to the command register. In I2C mode, this pulled low is pulled low. |                             |                            |  |  |  |

|         |              | acts as SA0 for slave                                                                                                                                                 | to the command register     | . In 12C mode, this pin    |  |  |  |

|         |              | address selection.                                                                                                                                                    |                             |                            |  |  |  |

|         |              |                                                                                                                                                                       | MCII interface signals r    | please refer to the Timing |  |  |  |

|         |              | Characteristics Diagrams                                                                                                                                              |                             | hease refer to the Tilling |  |  |  |

|         |              | Read/Write Select or Wr                                                                                                                                               |                             |                            |  |  |  |

|         |              | 1                                                                                                                                                                     |                             | a to a 68VV somios         |  |  |  |

|         |              | This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as Read/Write (R/W#) selection                               |                             |                            |  |  |  |

|         |              | input. Pull this pin to "H                                                                                                                                            |                             |                            |  |  |  |

| 11      | R/W#         | 1 1                                                                                                                                                                   | ngn for read mode and       | pun it to Low for          |  |  |  |

| 11      | K/ W#        | write mode.                                                                                                                                                           | - d- (14, 1 d)              | .:11 1 41 W.:'- (WD !/\    |  |  |  |

|         |              | When 80XX interface me                                                                                                                                                |                             |                            |  |  |  |

|         |              | input. Data write operation                                                                                                                                           | on is initiated when this p | om is pulled low and the   |  |  |  |

|         |              | CS# is pulled low.                                                                                                                                                    |                             | 4 1 1 4 V/QQ               |  |  |  |

|         |              | When serial or I2C mode                                                                                                                                               | is selected, this pin mus   | t be connected to VSS.     |  |  |  |

| 12    | E/RD#      | Read/Write Enable or Read This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the CS# is pulled low. When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low.                                                                                                      |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

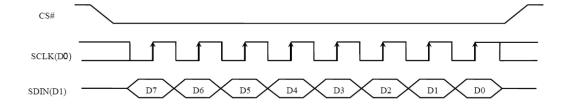

| 13-20 | D0-D7      | When serial or I2C mode is selected, this pin must be connected to VSS.  Host Data Input/ Output Bus These pins are 8-bit bi-directional data bus to be connected to the microprocessor's data bus. When serial mode is selected, D1 will be the serial data input SDIN and D0 will be the serial clock input SCLK. When I2C mode is selected, D2 & D1 should be tired together and serve as SDAout & SDAin in application and D0 is the serial clock input SCL. Unused pins must be connected to VSS except for D2 in serial mode. |

| 21    | IREF       | Current Reference for Brightness Adjustment This pin is segment current reference pin. A resistor should be connected between this pin and VSS. Set the current at 12.5 µ A maximum.                                                                                                                                                                                                                                                                                                                                                |

| 22    | VCOMH      | Voltage Output High Level for COM Signal This pin is the input pin for the voltage output high level for COM signals. A capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                                                                                                                     |

| 23    | VCC        | Power Supply for OEL Panel This is the most positive voltage supply pin of the chip. A stabilization capacitor should be connected between this pin and VSS when the converter is used. It must be connected to external source when the converter is not used.                                                                                                                                                                                                                                                                     |

| 24    | N.C. (GND) | Reserved Pin(Supporting Pin) The supporting pins can reduce the influences from stresses on the function pins. These pins must be connected to external ground as the ESD protection circuit.                                                                                                                                                                                                                                                                                                                                       |

## 3.2 Module Pin Description

| Pin No. | Symbol | Function Description                                             |

|---------|--------|------------------------------------------------------------------|

| 1       | GND    | Ground                                                           |

| 2       | VCC    | Power Supply 3.3V                                                |

| 3       | SCL    | SPI Clock                                                        |

| 4       | SDA    | SPI DATA                                                         |

| 5       | RES    | OLED reset Pin.                                                  |

| 6       | D/C    | Data/Command Control                                             |

| 0       | D/C    | This pin is Data/Command control pin.                            |

| 7       | CS     | Chip Select                                                      |

| /       | CS     | This pin is pulled low to active. Connect to ground if no used . |

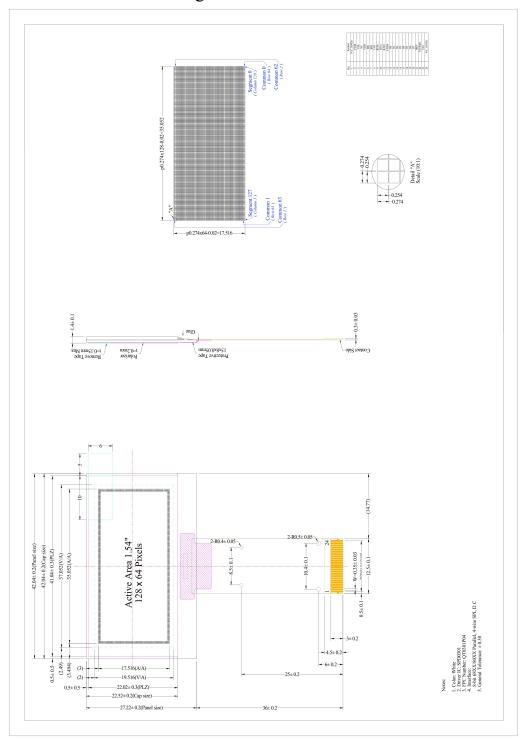

# 4 Mechanical Drawing

## 4.1 Panel Mechanical Drawing

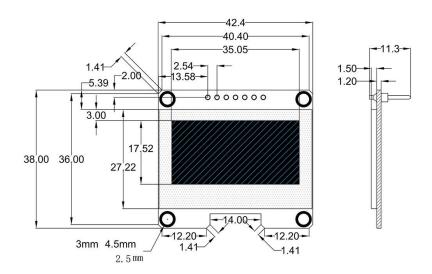

#### 4.2 Module Mechanical Drawing

#### 5 Electrical Characteristics

| Item                                       | Symbol | Condition       | Min  | Тур. | Max  | Unit |

|--------------------------------------------|--------|-----------------|------|------|------|------|

| Power supply                               | VDD    |                 | 2.6  | 3.3  | 3.5  | V    |

| Input Power                                | VCC IN |                 | 4.5  |      | 6.5  | V    |

| Supply Voltage for Display(for OLED Panel) | Vcc    |                 | 11.5 | 12   | 12.5 | V    |

| Segment Output current consumption in Vcc  | ISEG   | Contrast<br>max | 280  | 310  | 340  | uA   |

| Operating Maximum Temperature              | TOP    |                 | -40  |      | 70   | °C   |

| Storage Maximum Temperature                | TST    |                 | -40  |      | 85   | °C   |

# 6 Optical Characteristics

| Item                     | Symbol  | Min    | Тур | Max | Unit  |

|--------------------------|---------|--------|-----|-----|-------|

| View Angles              |         | 160    |     | -   | 0     |

| Response Time (25°C)     | Tr + Tf |        | 30  |     | ns    |

| Brightness               | Lbr     | 90     | 110 | -   | cd/m² |

| Dark room Contrast Ratio | CR      | 2000:1 | -   | -   |       |

## 7 AC characteristics

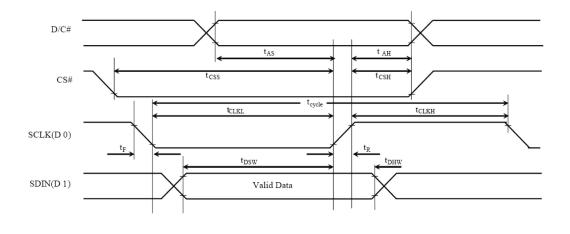

## 7.1 Serial Interface Timing Characteristics (4-wire SPI)

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 250 | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 150 | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 150 | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 120 | _   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 60  | _   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 50  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | _   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 100 | _   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 100 | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 1.65V \text{ to } 3.3V, VDD=VDDIO, T_a = 25^{\circ}C)$

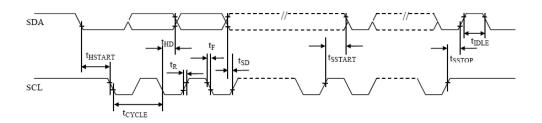

#### 7.2 I2C interface characteristics

| Symbol              | Description                                                               | Min | Max | Unit |

|---------------------|---------------------------------------------------------------------------|-----|-----|------|

| t <sub>cycle</sub>  | Clock Cycle Time                                                          | 2.5 | -   | μs   |

| t <sub>HSTART</sub> | Start Condition Hold Time                                                 | 0.6 | _   | μs   |

| _                   | Data Hold Time (for "SDA <sub>OUT</sub> " Pin)                            | 0   |     |      |

| t <sub>HD</sub>     | Data Hold Time (for "SDA <sub>IN</sub> " Pin)                             | 300 | _   | ns   |

| t <sub>SD</sub>     | Data Setup Time                                                           | 100 | _   | ns   |

| t <sub>SSTART</sub> | Start Condition Setup Time (Only relevant for a repeated Start condition) | 0.6 | -   | μs   |

| t <sub>SSTOP</sub>  | Stop Condition Setup Time                                                 | 0.6 | -   | μs   |

| t <sub>R</sub>      | Rise Time for Data and Clock Pin                                          |     | 300 | ns   |

| t <sub>F</sub>      | Fall Time for Data and Clock Pin                                          |     | 300 | ns   |

| t <sub>IDLE</sub>   | Idle Time before a New Transmission can Start                             | 1.3 | _   | μs   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 1.65V \text{ to } 3.3V, T_a = 25^{\circ}C)$

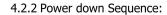

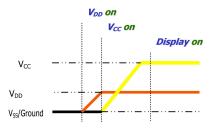

#### 8 Power on/off sequence

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

#### 4.2.1 Power up Sequence:

- 1. Power up  $V_{\text{DD}}$

- 2. Send Display off command

- 3. Initialization

- 4. Clear Screen

- 5. Power up V<sub>CC</sub>

- 6. Delay 100ms (When V<sub>CC</sub> is stable)

- 7. Send Display on command

- 1. Send Display off command

- 2. Power down  $V_{\text{CC}}$

- 3. Delay 100ms (When  $V_{CC}$  is reach 0 and panel is completely discharges)

- 4. Power down V<sub>DD</sub>

#### Note 13:

- 1) Since an ESD protection circuit is connected between  $V_{DD}$  and  $V_{CC}$  inside the driver IC,  $V_{CC}$  becomes lower than  $V_{DD}$  whenever  $V_{DD}$  is ON and  $V_{CC}$  is OFF.

- 2)  $V_{CC}$  should be kept float (disable) when it is OFF.

- 3) Power Pins ( $V_{DD}$ ,  $V_{CC}$ ) can never be pulled to ground under any circumstance.

- 4)  $V_{DD}$  should not be power down before  $V_{CC}$  power down.

## 9 Schematic

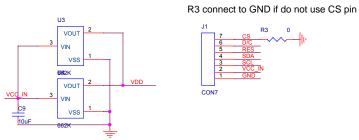

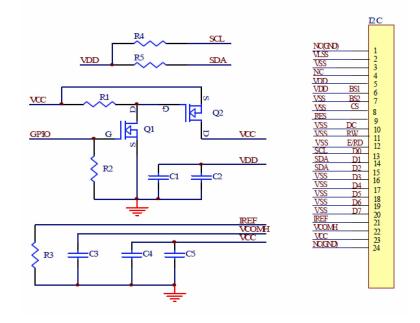

#### 9.1 Module schematic

##

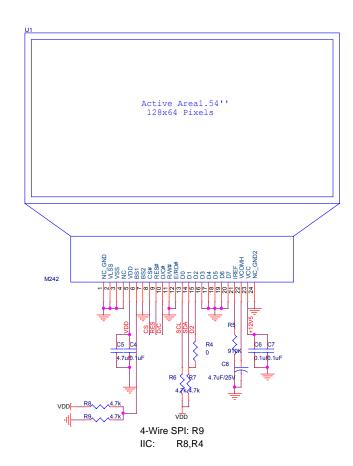

#### 9.2 Application circuit for 4-wire SPI mode

(When design main board, Please add Electronic Switch circuit, otherwise, will be caused leak current)

#### **Recommended Components:**

C1, C2:  $1\mu$ F / 16V, X5R C3:  $2.2\mu$ F /25V C4:  $4.7\mu$ F / 25V, X7R C5:  $0.1\mu$ F / 25V, X7R

R1, R2: 47kΩ

R3:  $910K\Omega$ , R3 = (Voltage at IREF - VSS) / IREF

Q2: FDN338P Q1: FDN335N

**Notes:**

VDD: 1.65V~3.3V VCC\_IN: 11.5~12.5V

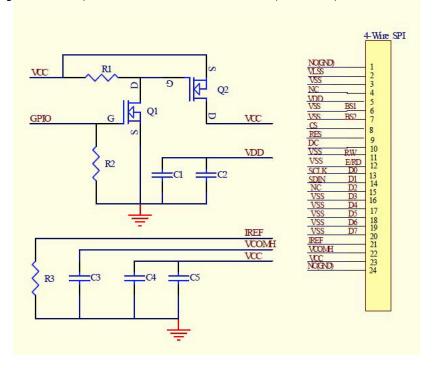

#### 9.3 Application circuit for IIC mode

(When design main board, Please add Electronic Switch circuit, otherwise, will be caused leak current)

#### **Recommended Components:**

C1, C2:  $1\mu F / 16V$ , X5R C3:  $2.2\mu F / 25V$ C4:  $4.7\mu F / 25V$ , X7R C5:  $0.1\mu F / 25V$ , X7R

R1, R2:  $47k\Omega$

R3:  $910K\Omega$ , R3 = (Voltage at IREF - VSS) / IREF

R4, R5: 4.7kΩ Q2: FDN338P Q1: FDN335N

Notes:

VDD: 1.65V~3.3V VCC\_IN: 11.5~12.5V

The  $I^2C$  slave address is 0111100b'. If the customer ties D/C# to VDD, the  $I^2C$  slave address will be

0111101b'.

#### 10 Command Table

Please check in driver IC DATASHEET

# 11 Reliability

| Test Item                | Content of Test                          | Test Condition | Note |

|--------------------------|------------------------------------------|----------------|------|

| High Temperature Storage | Endurance test applying the high storage | 85°C           | 2    |

|                          | temperature for a long time.                 | 200hrs             |     |

|--------------------------|----------------------------------------------|--------------------|-----|

| Low Temperature Storage  | Endurance test applying the high storage     | -40°C              | 1.2 |

|                          | temperature for a long time.                 | 200hrs             | 1,2 |

| High Temperature         | Endurance test applying the electric stress  | 70°C               |     |

| Operation                | (Voltage & Current) and the thermal stress   | 200hrs             | -   |

|                          | to the element for a long time.              |                    |     |

| Low Temperature          | Endurance test applying the electric stress  | -40 °C             | 1   |

| Operation                | under low temperature for a long time.       | 200hrs             | 1   |

| High Temperature/        | The module should be allowed to stand at     | 60°C,90%RH         |     |

| Humidity Operation       | 60°C,90%RH max, for 96hrs under no-load      | 96hrs              |     |

|                          | condition excluding the polarizer. Then      |                    | 1,2 |

|                          | taking it out and drying it at normal        |                    |     |

|                          | temperature.                                 |                    |     |

| Thermal Shock Resistance | The sample should be allowed stand the       | -40°C/85°C         |     |

|                          | following 10 cycles of operation             | 10 cycles          |     |

|                          | -40°C 25°C 85°C√                             |                    |     |

|                          |                                              |                    | -   |

|                          | 20i 20i-                                     |                    |     |

|                          | 30min 5min 30min-                            |                    |     |

|                          | 1 cycle₽                                     |                    |     |

| Vibration Test           | Endurance test applying the vibration during | Total fixed        |     |

|                          | transportation and using                     | amplitude:         |     |

|                          |                                              | 15mm; Vibration:   |     |

|                          |                                              | 10~55Hz;           |     |

|                          |                                              | One cycle 60       | 3   |

|                          |                                              | seconds to 3       |     |

|                          |                                              | directions of X,   |     |

|                          |                                              | Y, Z, for each 16  |     |

|                          |                                              | minutes.           |     |

| Static Electricity Test  | Endurance test apply the electric stress to  | VS=800V,           |     |

|                          | the terminal.                                | RS=1.5k $\Omega$ , | _   |

|                          |                                              | CS=100pF,          | _   |

|                          |                                              | 1 time.            |     |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal. Temperature and humidity after remove from the rest chamber.

Note3: Test performed on product itself, not inside a container.

## 12 Warranty and Conditions

http://www.displaymodule.com/pages/faq HYPERLINK

"http://www.displaymodule.com/pages/faq"